1. Vorwort zum PCB-Design

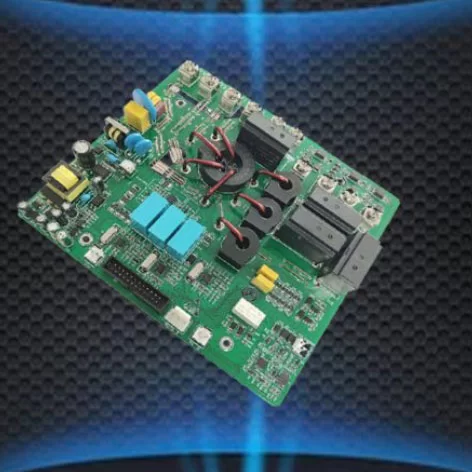

Mit dem zunehmenden Wettbewerb auf dem Markt für Kommunikations- und Elektronikprodukte verkürzt sich der Lebenszyklus von Produkten. Die Aktualisierung von Originalprodukten und die Veröffentlichungsgeschwindigkeit neuer Produkte spielen eine immer wichtigere Rolle für das Überleben und die Entwicklung des Unternehmens. Im Fertigungsbereich wird die Frage, wie man neue Produkte mit höherer HersTellbarkeit und Fertigungsqualität mit kürzerer Vorlaufzeit in der Produktion erhält, immer mehr zum Wettbewerbsziel von Menschen mit Visionen.

Bei der HersTellung elektronischer Produkte wird mit der Miniaturisierung und Komplexität der Produkte die Bestückungsdichte von Leiterplatten immer höher. Dementsprechend erfordert die neue Generation des SMT-Montageprozesses, der weit verbreitet ist, dass Designer von Anfang an die HersTellbarkeit berücksichtigen. Sobald die schlechte HersTellbarkeit auf eine schlechte Berücksichtigung des Designs zurückzuführen ist, muss das Design geändert werden, was unweigerlich die Zeit der Produkteinführung verlängert und die Einführungskosten erhöht. Selbst wenn das PCB-Layout geringfügig geändert wird, belaufen sich die Kosten für die Neuanfertigung der Leiterplatte und der SMT-Lötpastendruck-Siebplatine auf Taue oder sogar Zehntaue Yuan, und die analoge Schaltung muss sogar erneut debuggt werden. Die Verzögerung der Importzeit kann dazu führen, dass das Unternehmen Marktchancen verpasst und sich strategisch in einer sehr nachteiligen Position befindet. Wenn das Produkt jedoch ohne Modifikation hergesTellt wird, weist es unweigerlich HersTellungsfehler auf oder erhöht die HersTellungskosten, was teurer wird. Wenn Unternehmen also neue Produkte entwerfen, ist es umso förderlicher für die effektive Einführung neuer Produkte, je früher die HersTellbarkeit des Designs berücksichtigt wird.

2. Beim PCB-Design zu berücksichtigende Inhalte

Die HersTellbarkeit des PCB-Designs ist in zwei Kategorien unterteilt: Die eine ist die Verarbeitungstechnologie zur HersTellung von Leiterplatten; Die zweite bezieht sich auf die Schaltung und Struktur der Komponenten und Leiterplatten des Montageprozesses. Für die Verarbeitungstechnologie zur HersTellung von Leiterplatten werden die Allegemeinen LeiterplattenhersTeller aufgrund des Einflusses ihrer Fertigungskapazität den Designern sehr detaillierte Anforderungen sTellen, was in der Praxis relativ gut ist. Doch nach dem Verständnis des Autors ist der zweite Typ, nämlich das HersTellbarkeitsdesign für elektronische Baugruppen, in der Praxis nicht ausreichend beachtet worden. Der Schwerpunkt dieses Dokuments liegt auch auf der Beschreibung der HersTellbarkeitsprobleme, die Designer in der Phase des PCB-Designs berücksichtigen müssen.

Das HersTellbarkeitsdesign für elektronische Baugruppen erfordert, dass PCB-Designer zu Beginn des PCB-Designs Folgendes berücksichtigen:

2.1 Geeignete Auswahl des Montagemodus und des Komponentenlayouts beim PCB-Design

Die Auswahl des Bestückungsmodus und des Komponentenlayouts ist ein sehr wichtiger Aspekt der HersTellbarkeit von Leiterplatten, der große Auswirkungen auf die Bestückungseffizienz, die Kosten und die Produktqualität hat. Tatsächlich ist der Autor mit vielen Leiterplatten in Berührung gekommen, und es mangelt immer noch an der Berücksichtigung einiger sehr grundlegender Prinzipien.

(1) Wählen Sie die entsprechende Montagemethode

Im Allegemeinen werden je nach Bestückungsdichte der Leiterplatte die folgenden Bestückungsmethoden empfohlen:

Montagemethode | Schematisch | Generalversammlungsprozess |

1 Einseitiger Voll-SMD |

| Einzelplatten-Lötpastendruck, Reflow-Löten nach der Platzierung |

2 Doppelseitiges Voll-SMD |

| A. Auf der B-Seite aufgedruckte Lötpaste, SMD-Reflow-Löten oder auf der B-Seite punktuelle (aufgedruckte) Klebemassen nach dem Spitzenlöten |

3 Einseitige Originalmontage |

| Gedruckte Lotpaste, Post-Placement-Reflow-Löten von SMD-armen zukünftigen Wellenlöten von perforierten Bauteilen |

4 gemischte Komponenten auf Seite A. Einfaches SMD nur auf Seite B |

| Gedruckte Lotpaste auf Seite A, SMD-Reflow-Löten; Nach dem Punktieren (Drucken) Kleben, Fixieren von SMD auf Seite B, Montieren von perforierten Bauteilen, Wellenlöten von THD und SMD auf Seite B |

5 Einfügen auf Seite A Einfaches SMD nur auf Seite B |

| Nach dem Aushärten des SMD mit punktuellem (gedrucktem) Kleber auf der B-Seite werden die perforierten Komponenten montiert und mit dem THD und dem B-seitigen SMD wellengelötet |

Als Schaltungsdesigner sollte ich den PCB-Montageprozess richtig verstehen, damit ich grundsätzlich einige Fehler vermeiden kann. Bei der Auswahl des Montagemodus müssen neben der Bestückungsdichte der Leiterplatte und der Schwierigkeit der Verkabelung auch der typische Prozessablauf dieses Montagemodus und der Grad der Prozessausrüstung des Unternehmens selbst berücksichtigt werden. Wenn das Unternehmen nicht über einen guten Wellenschweißprozess verfügt, kann die Wahl der fünften Montagemethode in der obigen Tabelle zu großen Problemen führen. Es ist auch erwähnenswert, dass, wenn der Wellenlötprozess für die Schweißoberfläche geplant ist, vermieden werden sollte, den Prozess durch die Platzierung einiger SMDS auf der Schweißoberfläche zu komplizieren.

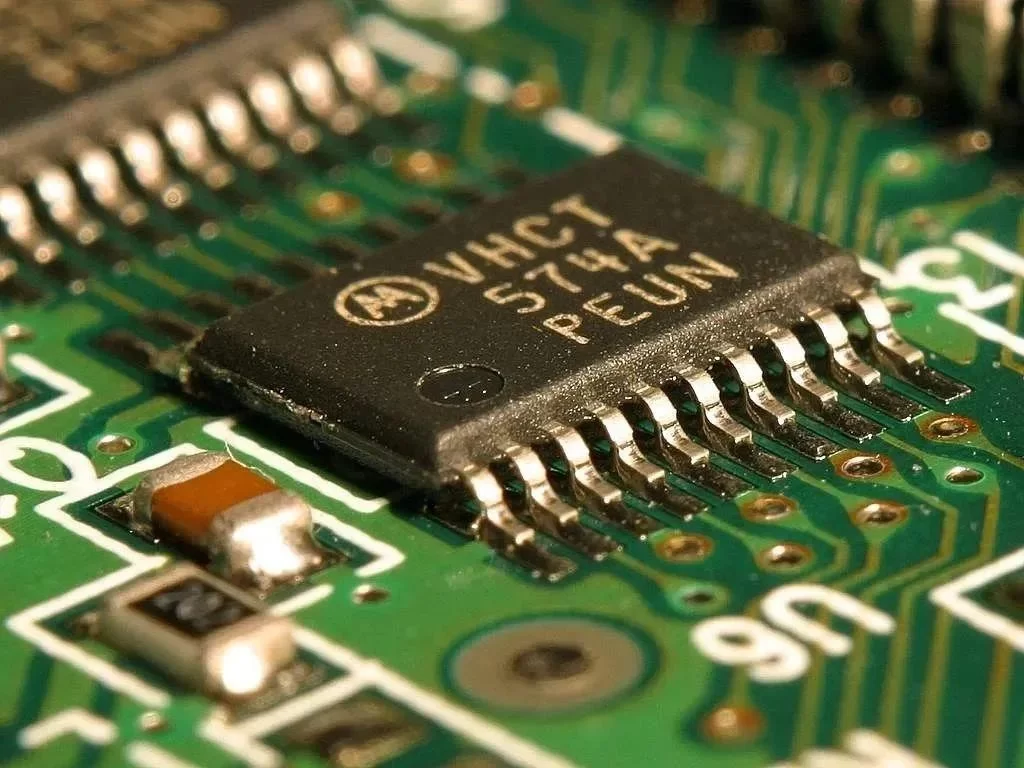

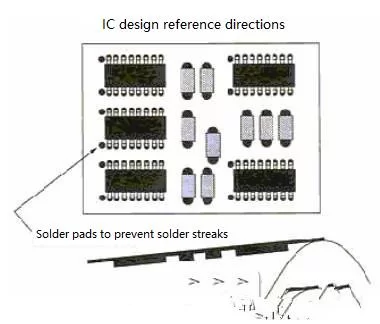

(2) Komponentenlayout

Das Layout von PCB-Komponenten hat einen sehr wichtigen Einfluss auf die Produktionseffizienz und -kosten und ist ein wichtiger Index zur Messung der Anschlussfähigkeit des PCB-Designs. Im Allegemeinen sind die Komponenten möglichst gleichmäßig, regelmäßig und sauber angeordnet und in der gleichen Richtung und Polaritätsverteilung angeordnet. Die regelmäßige Anordnung ist praktisch für die Inspektion und trägt zur Verbesserung der Patch-/Einsteckgeschwindigkeit bei, eine gleichmäßige Verteilung trägt zur Wärmeableitung und zur Optimierung des Schweißprozesses bei. Um den Prozess zu vereinfachen, sollten sich PCB-Designer andererseits immer darüber im Klaren sein, dass auf beiden Seiten der PCB nur ein Gruppenschweißprozess aus Reflow-Schweißen und Wellenschweißen verwendet werden kann. Dies macht sich insbesondere bei der Bestückungsdichte bemerkbar, da die Leiterplatten-Schweißfläche mit mehr Patch-Komponenten verteilt werden muss. Der Konstrukteur sollte überlegen, welches Gruppenschweißverfahren für die montierten Komponenten auf der Schweißfläche verwendet werden soll. Vorzugsweise kann ein Wellenlötprozess nach der Patch-Aushärtung verwendet werden, um gleichzeitig die Stifte der perforierten Vorrichtungen auf der Bauteiloberfläche zu verschweißen. Wellenschweiß-Patchkomponenten unterliegen jedoch relativ strengen Einschränkungen, nur Chipfestigkeit der Größe 0603 und höher, SOT-, SOIC-Schweißen (Stiftabstand ≥ 1 mm und Höhe weniger als 2,0 mm). Bei Bauteilen, die auf der Schweißfläche verteilt sind, sollte die Ausrichtung der Stifte beim Wellenkammschweißen senkrecht zur Übertragungsrichtung der Leiterplatte erfolgen, um sicherzusTellen, dass die Schweißenden bzw. Leitungen auf beiden Seiten der Bauteile gleichzeitig in die Schweißung eingetaucht werden. Auch die Anordnungsreihenfolge und Abstände zwischen benachbarten Bauteilen sollten den Anforderungen des Wellenkammschweißens genügen, um den „Abschirmeffekt“, wie in Abb. 1 dargesTellt, zu vermeiden. 1. Beim Wellenlöten von SOIC und anderen mehrpoligen Bauteilen sollten zwei (auf jeder Seite 1) Lötfüße in Richtung des Zinnflusses eingesTellt werden, um ein kontinuierliches Schweißen zu verhindern.

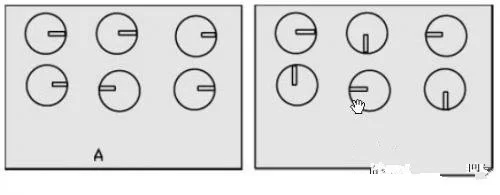

Komponenten ähnlichen Typs sollten in der gleichen Richtung auf der Platine angeordnet sein, um die Montage, Inspektion und das Schweißen der Komponenten zu erleichtern. Wenn beispielsweise die negativen Anschlüsse Alleer Radialkondensatoren zur rechten Seite der Platte zeigen, Allee DIP-Kerben in die gleiche Richtung zeigen usw., kann dies die Instrumentierung beschleunigen und das Auffinden von Fehlern erleichtern. Da Platine A diese Methode anwendet, ist es, wie in Abbildung 2 dargesTellt, einfacher, den Umkehrkondensator zu finden, während Platine B mehr Zeit benötigt, um ihn zu finden. Tatsächlich kann ein Unternehmen die Ausrichtung Alleer von ihm hergesTellten Leiterplattenkomponenten standardisieren. Bei einigen Platinenlayouts ist dies möglicherweise nicht unbedingt möglich, es sollte jedoch ein Aufwand sein.

Welche HersTellbarkeitsaspekte sollten beim PCB-Design berücksichtigt werden?

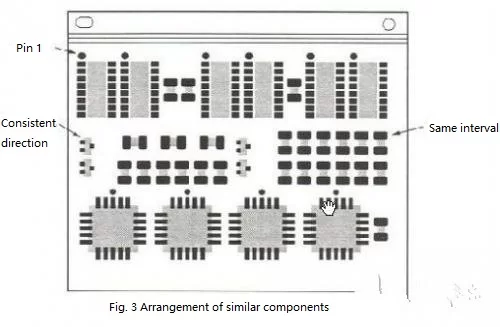

Außerdem sollten ähnliche Komponententypen so weit wie möglich gemeinsam geerdet werden, wobei Allee Komponentenfüße in die gleiche Richtung weisen sollten, wie in Abbildung 3 dargesTellt.

Alleerdings ist der Autor tatsächlich auf eine ganze Reihe von Leiterplatten gestoßen, bei denen die Bestückungsdichte zu hoch ist und die Schweißfläche der Leiterplatte auch mit hohen Komponenten wie Tantalkondensatoren und Patch-Induktivitäten sowie dünn beabstandeten SOIC und TSOP verteilt werden muss. In diesem FAlle ist es nur möglich, doppelseitig bedruckte Lotpastenpflaster zum Rückflussschweißen zu verwenden, und Steckkomponenten sollten so weit wie möglich in der Komponentenverteilung konzentriert werden, um sie an das manuelle Schweißen anzupassen. Eine andere Möglichkeit besteht darin, die perforierten Elemente auf der Bauteilfläche möglichst in wenigen Hauptgeraden zu verteilen, um dem selektiven Wellenlötprozess Rechnung zu tragen, wodurch manuelles Schweißen vermieden, die Effizienz verbessert und die Qualität des Schweißens sichergesTellt werden kann. Die diskrete Verteilung der LötsTellen ist ein großes Tabu beim selektiven Wellenlöten, was die Verarbeitungszeit vervielfacht.

Beim Anpassen der Position von Komponenten in der Leiterplattendatei muss auf die Eins-zu-eins-Entsprechung zwischen Komponenten und Siebdrucksymbolen geachtet werden. Wenn die Komponenten bewegt werden, ohne dass die Siebdrucksymbole neben den Komponenten entsprechend verschoben werden, sTellt dies ein großes Qualitätsrisiko in der Fertigung dar, da in der tatsächlichen Produktion Siebdrucksymbole die Branchensprache sind, die die Produktion leiten kann.

2.2 Die Leiterplatte muss mit den für die automatische Fertigung erforderlichen Klemmkanten, Positionierungsmarkierungen und Prozesspositionierungslöchern ausgestattet sein.

Derzeit ist die elektronische Montage eine der Industrien mit einem hohen Automatisierungsgrad. Die in der Produktion verwendeten Automatisierungsgeräte erfordern eine automatische Übertragung der Leiterplatte, so dass die Übertragungsrichtung der Leiterplatte (im Allegemeinen für die Längsseitenrichtung) oben und unten jeweils eine nicht weniger als 3–5 mm breite Klemmkante aufweist.

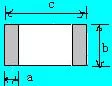

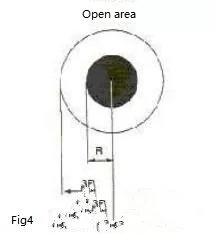

Die Rolle von Positionierungsmarkierungen besteht darin, dass die Leiterplatte mindestens zwei oder drei Positionierungsmarkierungen für das optische Identifikationssystem bereitsTellen muss, um die Leiterplatte genau zu lokalisieren und Leiterplattenbearbeitungsfehler für die Montageausrüstung zu korrigieren, die bei der optischen Positionierung häufig verwendet wird. Von den üblicherweise verwendeten Positionierungsmarkierungen müssen zwei auf der Diagonale der Leiterplatte verteilt sein. Bei der Auswahl der Positionierungsmarkierungen werden im Allegemeinen Standardgrafiken verwendet, z. B. ein solides rundes Pad. Um die Identifizierung zu erleichtern, sollte um die Markierungen herum ein leerer Bereich ohne andere Schaltkreismerkmale oder Markierungen vorhanden sein, dessen Größe nicht kleiner als der Durchmesser der Markierungen sein sollte (wie in Abbildung 4 dargesTellt), und der Abstand zwischen den Markierungen und der Kante der Platine sollte mehr als 5 mm betragen.

Bei der HersTellung von Leiterplatten selbst sowie im Montageprozess von halbautomatischen Plug-Ins, IKT-Tests und anderen Prozessen muss die Leiterplatte in den Ecken zwei bis drei Positionierungslöcher vorsehen.

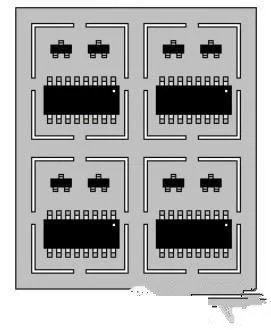

2.3 Rationeller Einsatz von Panels zur Verbesserung der Produktionseffizienz und -flexibilität

Beim Zusammenbau von Leiterplatten mit kleinen Abmessungen oder unregelmäßigen Formen gelten viele Einschränkungen. Daher wird im Allegemeinen angenommen, dass mehrere kleine Leiterplatten zu Leiterplatten geeigneter Größe zusammengebaut werden, wie in Abbildung 5 dargesTellt. Im Allegemeinen kann bei Leiterplatten mit einer Einzelseitengröße von weniger als 150 mm die Verwendung der Spleißmethode in Betracht gezogen werden. Durch zwei, drei, vier usw. kann die Größe großer Leiterplatten an den entsprechenden Verarbeitungsbereich gespleißt werden. Im Allegemeinen ist eine Leiterplatte mit einer Breite von 150 mm bis 250 mm und einer Länge von 250 mm bis 350 mm die geeignetere Größe für die automatische Montage.

Eine andere Art der Platine besteht darin, die Leiterplatte mit SMD auf beiden Seiten einer positiven und negativen Schreibweise in einer großen Platine anzuordnen. Eine solche Platine wird Allegemein als Yin und Yang bezeichnet, im Allegemeinen aus Gründen der Kostenersparnis für die Schirmplatine, das heißt, durch eine solche Platine waren ursprünglich zwei Seiten der Schirmplatine erforderlich, jetzt muss nur noch eine Schirmplatine geöffnet werden. Wenn die Techniker außerdem das laufende Programm der SMT-Maschine vorbereiten, ist auch die PCB-Programmiereffizienz von Yin und Yang höher.

Wenn die Platine geteilt ist, kann die Verbindung zwischen den Unterplatinen aus doppelseitigen V-förmigen Rillen, langen Schlitzlöchern und runden Löchern usw. bestehen. Bei der Konstruktion muss jedoch darauf geachtet werden, dass die Trennlinie so weit wie möglich in einer geraden Linie verläuft, um die Platine zu erleichtern. Beachten Sie aber auch, dass die Trennseite nicht zu nahe an der Leiterplattenlinie liegen darf, damit die Leiterplatte bei der Platine leicht beschädigt werden kann.

Es handelt sich auch um eine sehr kostengünstige Platine und bezieht sich nicht auf die Leiterplatte, sondern auf die Maschen der Rastergrafikplatine. Durch den Einsatz einer automatischen Lotpastendruckmaschine hat die aktuelle, fortschrittlichere Druckmaschine (z. B. DEK265) die Größe von 790 × 790 mm Stahlgewebe ermöglicht, ein mehrseitiges PCB-Netzmuster eingerichtet und ein Stück Stahlgewebe für den Druck mehrerer Produkte erhalten. Dies ist eine sehr kostensparende Praxis, die sich besonders für die Produkteigenschaften von Kleinserien und verschiedenen HersTellern eignet.

2.4 Überlegungen zum Testbarkeitsdesign

Das Testbarkeitsdesign von SMT ist hauptsächlich auf die aktuelle IKT-Ausrüstungssituation ausgerichtet. Prüfaspekte für die Postproduktionsfertigung werden bei Schaltungs- und oberflächenmontierten Leiterplatten-SMB-Designs berücksichtigt. Um das Testbarkeitsdesign zu verbessern, sollten zwei Anforderungen des Prozessdesigns und des elektrischen Designs berücksichtigt werden.

2.4.1 Anforderungen an die Prozessgestaltung

Die Genauigkeit der Positionierung, das SubstrathersTellungsverfahren, die Substratgröße und der Sondentyp sind Faktoren, die sich auf die Zuverlässigkeit der Sonde auswirken.

(1) Positionierungsloch. Der Fehler bei der Positionierung der Löcher auf dem Substrat sollte innerhalb von ±0,05 mm liegen. Setzen Sie mindestens zwei Positionierungslöcher möglichst weit auseinander. Die Verwendung von nichtmetAlleischen Positionierungslöchern zur Reduzierung der Dicke der Lotbeschichtung kann die Toleranzanforderungen nicht erfüllen. Wenn das Substrat als Ganzes hergesTellt und dann separat getestet wird, müssen sich die Positionierungslöcher auf der Hauptplatine und jedem einzelnen Substrat befinden.

(2) Der Durchmesser des Testpunkts beträgt nicht weniger als 0,4 mm und der Abstand zwischen benachbarten Testpunkten beträgt mehr als 2,54 mm und nicht weniger als 1,27 mm.

(3) Komponenten mit einer Höhe von mehr als *mm sollten nicht auf der Testoberfläche platziert werden, da dies zu einem schlechten Kontakt zwischen der Sonde der Online-Testvorrichtung und dem Testpunkt führen würde.

(4) Platzieren Sie den Testpunkt 1,0 mm von der Komponente entfernt, um eine Beschädigung durch Stöße zwischen der Sonde und der Komponente zu vermeiden. Im Umkreis von 3,2 mm um den Ring des Positionierungslochs dürfen sich keine Komponenten oder Testpunkte befinden.

(5) Der Prüfpunkt darf nicht weiter als 5 mm von der Leiterplattenkante entfernt liegen, die zur Gewährleistung der Klemmbefestigung dient. In Förderbandproduktionsanlagen und SMT-Anlagen ist in der Regel die gleiche Prozesskante erforderlich.

(6) Allee Erfassungspunkte müssen aus verzinnten oder metAlleischen leitfähigen Materialien mit weicher Textur, leichter Penetration und Nichtoxidation bestehen, um einen zuverlässigen Kontakt zu gewährleisten und die Lebensdauer der Sonde zu verlängern.

(7) Der Testpunkt darf nicht mit LötmitTel oder Texttinte abgedeckt werden, da sonst die Kontaktfläche des Testpunkts verringert und die Zuverlässigkeit des Tests verringert wird.

2.4.2 Anforderungen an die Elektrokonstruktion

(1) Der SMC/SMD-Testpunkt der Bauteiloberfläche sollte so weit wie möglich durch das Loch zur Schweißfläche geführt werden und der Lochdurchmesser sollte größer als 1 mm sein. Auf diese Weise können einseitige Nadelbetten für Online-Tests verwendet werden, wodurch die Kosten für Online-Tests gesenkt werden.

(2) Jeder elektrische Knoten muss einen Testpunkt haben, und jeder IC muss einen Testpunkt für POWER und GROUND haben, und zwar so nah wie möglich an dieser Komponente, innerhalb eines Bereichs von 2,54 mm vom IC.

(3) Die Breite des Testpunkts kann auf eine Breite von 40 mil vergrößert werden, wenn er auf dem Schaltkreis platziert wird.

(4) Verteilen Sie die Testpunkte gleichmäßig auf der Leiterplatte. Wenn die Sonde in einem bestimmten Bereich konzentriert ist, verformt der höhere Druck die zu prüfende Platte oder das Nadelbett und verhindert so, dass ein Teil der Sonde den Testpunkt erreicht.

(5) Die Stromversorgungsleitung auf der Leiterplatte sollte in Bereiche unterteilt werden, um den Testhaltepunkt festzulegen, damit der Fehlerpunkt schneller und genauer gefunden werden kann, wenn der Leistungsentkopplungskondensator oder andere Komponenten auf der Leiterplatte einen Kurzschluss zur Stromversorgung aufweisen. Bei der Gestaltung von Haltepunkten sollte die Strombelastbarkeit nach Wiederaufnahme des Testhaltepunkts berücksichtigt werden.

Abbildung 6 zeigt ein Beispiel für ein Testpunktdesign. Das Testpad wird über das Verlängerungskabel in der Nähe der Leitung des Bauteils angebracht oder der Testknoten wird über das perforierte Pad verwendet. Es ist strengstens verboten, den Testknoten an der LötsTelle des Bauteils auszuwählen. Bei dieser Prüfung kann es sein, dass sich die virtuelle Schweißverbindung unter dem Druck der Sonde in die ideale Position ausdehnt, sodass der virtuelle Schweißfehler verdeckt wird und der sogenannte „Fehlermaskierungseffekt“ auftritt. Aufgrund der durch den Positionierungsfehler verursachten Vorspannung der Sonde kann die Sonde direkt auf den Endpunkt oder Stift der Komponente einwirken, was zu Schäden an der Komponente führen kann.

Welche HersTellbarkeitsaspekte sollten beim PCB-Design berücksichtigt werden?

3. Schlussbemerkungen zum PCB-Design

Dies sind einige der Hauptprinzipien, die beim PCB-Design berücksichtigt werden sollten. Bei der HersTellung von Leiterplatten, die auf die elektronische Montage ausgerichtet sind, gibt es eine ganze Reihe von Details, wie z. B. die angemessene Anordnung des pasen Raums mit den Strukturteilen, die angemessene Verteilung von Siebdruckgrafiken und -texten, die angemessene Verteilung der Standorte schwerer oder großer Heizgeräte. In der Entwurfsphase der Leiterplatte ist es notwendig, den Testpunkt und den Testraum an der richtigen Position einzurichten und die Interferenzen zwischen der Matrize und den in der Nähe verteilten Komponenten zu berücksichtigen, wenn die Kupplungen durch den Zug- und Pressnietprozess instAlleiert werden. Ein PCB-Designer berücksichtigt nicht nur, wie man eine gute elektrische Leistung und ein schönes Layout erreicht, sondern auch einen ebenso wichtigen Punkt, nämlich die HersTellbarkeit beim PCB-Design, um hohe Qualität, hohe Effizienz und niedrige Kosten zu erreichen.