Zweck der Impedanzkontrolle

Ermittlung der Anforderungen an die Impedanzkontrolle, Standardisierung der Impedanzberechnungsmethode, Formulierung der Richtlinien für das COUPON-Design für Impedanztests und SichersTellung, dass die Produkte den Produktionsanforderungen und Kundenanforderungen entsprechen können.

Definition der Impedanzkontrolle

Definition der Impedanz

Bei einer bestimmten Frequenz überträgt die SignAlleeitung eines elektronischen Geräts relativ zu einer Referenzschicht ihr Hochfrequenzsignal oder ihre elektromagnetische Welle im Ausbreitungsprozess einen Widerstand, der als charakteristische Impedanz bezeichnet wird und eine Vektorsumme aus elektrischer Impedanz, induktivem Widerstand und kapazitivem Widerstand ist.

Klassifizierung der Impedanz

Derzeit ist unsere gemeinsame Impedanz unterteilt in: Single-Ended-Impedanz (Leitungsimpedanz), Differentialimpedanz (dynamische Impedanz) und Common-Impedanz

Impedanz dieser drei Fälle

1. Single-Ended-(Leitungs-)Impedanz: Englische Single-Ended-Impedanz, bezieht sich auf die von einer einzelnen SignAlleeitung gemessene Impedanz.

2. Differenzielle (dynamische) Impedanz: Englische Differenzimpedanz, bezieht sich auf die differenzielle Ansteuerung von zwei Übertragungsleitungen gleicher Breite und gleichem Abstand, die auf die Impedanz getestet wurden.

3. Koplanare Impedanz: Englische koplanare Impedanz, bezieht sich auf die SignAlleeitung in der Umgebung von GND/VCC (SignAlleeitung zu ihren beiden Seiten von GND/VCC). Die Impedanz wird bei der Übertragung zwischen GND/VCC (gleicher Abstand zwischen der SignAlleeitung und ihren beiden Seiten von GND/VCC) getestet.

Die Anforderungen an die Impedanzkontrolle werden durch die folgenden Bedingungen bestimmt

Wenn das Signal im PCB-Leiter übertragen wird und die Länge des Drahts etwa 1/7 der Signalwellenlänge beträgt, wird der Draht zu einem Signal

PCB-Produktion, entsprechend den Kundenanforderungen, um zu entscheiden, ob die Impedanz gesteuert werden soll

Wenn der Kunde eine Leitungsbreite für die Impedanzsteuerung benötigt, muss die Produktion die Impedanz der Leitungsbreite steuern.

Drei Elemente der Impedanzanpassung:

Ausgangsimpedanz (ursprünglicher aktiver Teil), charakteristische Impedanz (SignAlleeitung) und Eingangsimpedanz (passiver Teil)

(PCB-Platine) Impedanzanpassung

Wenn das Signal auf der Leiterplatte übertragen wird, muss die charakteristische Impedanz der Leiterplatte mit der elektronischen Impedanz der Kopf- und Schwanzkomponenten übereinstimmen. Sobald der Impedanzwert außerhalb der Toleranz liegt, wird die übertragene Signalenergie reflektiert, gestreut, gedämpft oder verzögert, was zu einem unvollständigen Signal und einer Signalverzerrung führt. Einflussfaktoren auf die Impedanz:

Er: dielektrische Permittivität, umgekehrt proportional zum Impedanzwert, Dielektrizitätskonstante gemäß der neu bereitgesTellten Berechnung der „Blatt-Dielektrizitätskonstantentabelle“.

H1, H2, H3 usw.: Leitungsschicht und Erdungsschicht sind zwischen der Mediendicke und dem Impedanzwert proportional.

W1: Breite der Impedanzleitung; W2: Impedanzlinienbreite und Impedanz ist umgekehrt proportional.

A: Wenn das innere Bodenkupfer für HOZ, W1 = W2 + 0,3 mil; inneres Bodenkupfer für 1OZ, W1 = W2 + 0,5mil; wenn das innere untere Kupfer für 2OZ W1 = W2 + 1,2mil.

B: Wenn das äußere Basiskupfer HOZ ist, ist W1=W2+0,8mil; wenn das äußere Basiskupfer 1OZ beträgt, W1=W2+1,2mil; Wenn das Kupfer der äußeren Basis 2OZ beträgt, ist W1=W2+1,6mil.

C: W1 ist die ursprüngliche Impedanzlinienbreite. T: Kupferdicke, umgekehrt proportional zum Impedanzwert.

A: Die innere Schicht ist die Kupferdicke des Substrats, HOZ wird mit 15 μm berechnet; 1OZ wird durch 30μm berechnet; 2OZ wird durch 65μm berechnet.

B: Die äußere Schicht besteht aus Kupferfoliendicke + Kupferbeschichtungsdicke, abhängig von den Lochkupferspezifikationen, wenn das untere Kupfer HOZ ist, Lochkupfer (durchschnittlich 20 μm, minimal 18 μm), das Tischkupfer berechnet mit 45 μm; Lochkupfer (durchschnittlich 25 μm, minimal 20 μm), das Tischkupfer berechnet um 50 μm; Lochkupfer-Einzelpunkt mindestens 25 μm, das Tischkupfer berechnet um 55 μm.

C: Wenn das untere Kupfer 1 Unze beträgt, Lochkupfer (durchschnittlich 20 μm, minimal 18 μm), wird das Tischkupfer mit 55 μm berechnet; Lochkupfer (durchschnittlich 25 μm, minimal 20 μm), das Tischkupfer wird mit 60 μm berechnet; Lochkupfer-Einzelpunkt mindestens 25 μm, das Tischkupfer wird mit 65 μm berechnet.

S: der Abstand zwischen benachbarten Leitungen und Leitungen, proportional zum Impedanzwert (Differenzimpedanz).

1. C1: Dicke des Substratlötwiderstands, umgekehrt proportional zum Impedanzwert;

2. C2: Dicke des Lötwiderstands der Leitungsoberfläche, umgekehrt proportional zum Impedanzwert;

3. C3: Zwischenliniendicke, umgekehrt proportional zum Impedanzwert;

4. CEr: Dielektrizitätskonstante des Lötstopplacks, und der Impedanzwert ist umgekehrt proportional zu .

A: Einmal gedruckte Lötstoppfarbe, C1-Wert 30 μm, C2-Wert 12 μm, C3-Wert 30 μm.

B: Zweimal gedruckte Lötstoppfarbe, C1-Wert 60 μm, C2-Wert 25 μm, C3-Wert 60 μm.

C: CEr: berechnet nach 3.4.

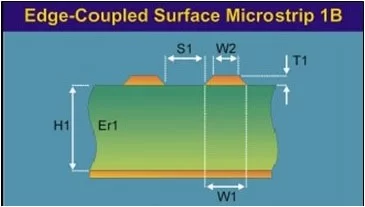

Anwendungsbereich: Differenzimpedanzberechnung vor dem äußeren Widerstandsschweißen

Parameterbeschreibung.

H1: Dielektrikumsdicke zwischen Außenschicht und VCC/GND

W2: Breite der Impedanzlinienoberfläche

W1: Untere Breite der Impedanzlinie

S1: Leitungslücke mit Differenzimpedanz

Er1: Dielektrizitätskonstante der dielektrischen Schicht

T1: Linienkupferdicke, einschließlich Substratkupferdicke + Beschichtungskupferdicke

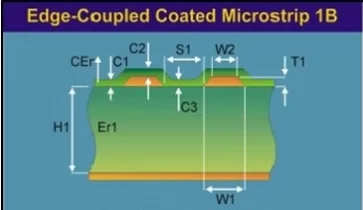

Anwendungsbereich: Differenzimpedanzberechnung nach äußerem Widerstandsschweißen

Parameterbeschreibung.

H1: Dicke des Dielektrikums zwischen Außenschicht und VCC/GND

W2: Breite der Impedanzlinienoberfläche

W1: Untere Breite der Impedanzlinie

S1: Leitungslücke mit Differenzimpedanz

Er1: Dielektrizitätskonstante der dielektrischen Schicht

T1: Linienkupferdicke, einschließlich Substratkupferdicke + Beschichtungskupferdicke

CEr: Dielektrizitätskonstante der Impedanz

C1: Dicke des Substratresists

C2: Dicke des Oberflächenlacks der Linie

C3: Differenzimpedanz-Interline-Resistdicke

Design des Impedanztests COUPON

GUTSCHEIN Standort hinzufügen

Der Impedanztest-COUPON wird im Allegemeinen in der Mitte der PNL platziert und darf nicht am Rand der PNL-Platine platziert werden, außer in Sonderfällen (z. B. 1PNL = 1PCS).

Überlegungen zum COUPON-Design

Um die Genauigkeit der Impedanztestdaten sicherzusTellen, muss das COUPON-Design die Form der Leitung innerhalb der Platine vollständig simulieren. Wenn die Impedanzleitung um die Platine durch Kupfer geschützt ist, sollte der COUPON so konzipiert sein, dass er die Schutzleitung ersetzt. Wenn die Platinenwiderstandslinie eine „Schlangen“-Ausrichtung aufweist, muss auch der COUPON als „Schlangen“-Ausrichtung ausgelegt sein. Wenn die Widerstandslinie im Board eine „Schlangen“-Ausrichtung aufweist, sollte auch der COUPON als „Schlangen“-Ausrichtung ausgelegt sein.

Impedanztest COUPON-Designspezifikationen

Single-Ended-(Leitungs-)Impedanz:

Testen Sie die wichtigsten COUPON-Parameter:

1. A: Testlochdurchmesser ∮ 1,20 mm (2X/COUPON), dies ist die Größe der Testersonde

2. B: Testpositionierungsloch: vereinheitlicht durch ∮2,0-mm-Produktion (3X/COUPON), Positionierung der Gongplatine mit; C: Zwei Testlochabstände von 3,58 mm

Differenzielle (dynamische) Impedanz

Hauptparameter des Test-COUPON: A: Testlochdurchmesser ∮ 1,20 mm (4X/COUPON), zwei davon für das SignAlleoch, die anderen beiden für das Erdungsloch, haben die Größe der Testersonde; B: Testpositionierungsloch: vereinheitlicht gemäß der Produktion von ∮ 2,0 MM (3X/COUPON), Positionierung der Gongplatine mit; C: Abstand zweier SignAlleöcher: 5,08 mm, Abstand zweier Erdungslöcher: 10,16 mm.

Gestalten Sie COUPON-Notizen

1. Der Abstand zwischen der Schutzleitung und der Impedanzleitung muss größer sein als die Breite der Impedanzleitung.

2. Die Länge der Impedanzleitung liegt im Allegemeinen im Bereich von 6 bis 12 Zoll.

3. Die nächstgelegene GND- oder POWER-Schicht der benachbarten Signalschicht ist die Erdungsreferenzschicht für die Impedanzmessung.

4. Die Schutzlinie der zwischen den beiden GND- und POWER-Schichten hinzugefügten SignAlleeitung sollte die SignAlleeitung einer Schicht zwischen den GND- und POWER-Schichten nicht verdecken.

5. Die beiden SignAlleöcher führen zur Differenzimpedanzleitung, und die beiden Erdungslöcher müssen gleichzeitig in der Referenzschicht geerdet werden.

6. Um die Gleichmäßigkeit der Kupferbeschichtung zu gewährleisten, ist es notwendig, an der äußeren Position der leeren Platine ein stromsparendes PAD oder eine Kupferhaut anzubringen.

Differenzielle koplanare Impedanz

Testen Sie die wichtigsten COUPON-Parameter: die gleiche Differenzimpedanz

Typ mit differenzieller koplanarer Impedanz:

1. Die Referenzschicht und die Impedanzleitung befinden sich auf derselben Ebene, das heißt, die Impedanzleitung ist vom umgebenden GND/VCC umgeben, und der umgebende GND/VCC ist der Referenzpegel. POLAR-Software-Berechnungsmodus, siehe 4.5.3.8; 4.5.3.9; 4.5.3.12.

2. Die Referenzschicht ist die GND/VCC-Schicht auf gleicher Ebene und die GND/VCC-Schicht neben der Signalschicht. (Die Impedanzleitung ist vom umgebenden GND/VCC umgeben und der umgebende GND/VCC ist die Referenzschicht).